# DC/DC Switching Power Converter with Digital Control based on FPGA

Ali Khajezadeh, Maysam Choobin

### Abstract

The paper first deals with the design of a DC/DC switching boost converter with digital control based on FPGAs, which is suitable for space applications. Digital control systems have significantly advantages over conventional pulse width modulator (PWM) controllers. Indeed, along with the general advantages of a digital system, such as reduced sensitivity to noise and component parameter variations, and the capability to realize sophisticated control algorithms, a digital controller can be hardened more easily against radiation-induced errors than its analog counterpart. Besides, the implementation of the digital controller in a SRAM FPGAs provides more flexibility in terms of quick turn-around time, and on-orbit reconfiguration capability. However, SRAM-based FPGAs are very sensitive to single-event effects (SEEs). Therefore, we propose a radiation-hardness-by-design (RHBD) technique based on logic duplication approach at both logic and device levels and on non-disruptive resynchronization mechanism that ensures the continuous operation of the converter when facing the issue of single-event functional interrupts (SEFIs) that may occur in SRAM-based FPGAs. This technique is validated with both VHDL simulations and experimental results.

Keywords: radiation-hardness-by-design, FPGAs, pulse width modulator, switching, DC/DC boost converter

### INTRODUCTION

DC/DC switching power converters, due to their high-efficiency conversion, are essential parts of the power conditioning system of a satellite [1]. The aim of this work is the design of a radiation hardened FPGA-based digital control system for a boost converter. Digital control systems have significant advantages over conventional analog pulse width modulators (PWMs). The use of commercial SRAM-based FPGAs in space applications is very attractive because of their high component density, quick turn-around time, and reconfigurability. However, SRAM-based FPGAs are very sensitive to SEEs. Indeed, along with the general advantages of a digital system (such as high flexibility, reduced sensitivity to noise and component parameter variations, and the capability to realize sophisticated control algorithms [2]), a digital controller can be hardened more easily against radiation-induced errors than its analog counterpart. In fact, a conventional PWM switching converter is very susceptible to single-event effects (SEEs) in the error

amplifier stage and in the analog PWM controller that cause large transient pulses at its output [3], [4].

The dominant effect is the single event functional interrupt (SEFI) caused to a configuration memory bit upset that disrupts the continuous operation of the system in which the FPGA is used. Heavy ion testing on these devices has shown that no permanent faults occur after a SEFI, and that reprogramming the FPGA will restore full functionality [5]. Therefore, "radiation hardening by design" (RHBD) techniques based on detecting, mitigating and correcting SEFIs make it possible to use SRAM-based FPGAs in space applications.

## DESIGN AND RESULTS

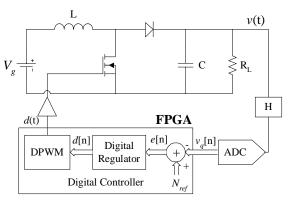

Fig 4.a shows the basic structure of a digitally controlled DC/DC switching boost converter. The actual output voltage v(t) is divided by the sensor gain (H) and converted into a digital signal  $v_q[n]$  by means of a sampling process and analog-to-digital conversion (ADC). The difference between the digitized sample of the converter output and the reference voltage ( $N_{rel}$ ) forms an error signal e[n] that is processed by the digital regulator to calculate the actual duty cycle d[n]. Eventually, the digital pulse width modulator (DPWM) generates the switching signal d(t) that controls the power MOSFET. In our design, we apply the 1-bit error resolution technique that uses a deadzone comparator to perform the A/D conversion and a simple up/down counter to calculate the duty cycle [7].

ali khajezadeh, department of electrical engineering, kerman branch,islamic azad university, kerman, iran; Email: alikhajezadeh@yahoo.com

maysam choobin, department of electrical engineering, kerman branch, islamic azad university, kerman, iran; meisam.chobin@gmail.com

To implement the digital controller in an SRAM-based FPGA, we apply a RHBD technique that mitigates and corrects SEFIs. When applying a digital control using an SRAM-based FPGA in a switching converter application, radiation induced SEFIs result in missing pulses in the generated PWM control signal of the converter. In turn, the missing pulses result in large transient voltage drops at the output of the converter that may adversely affect the operation of the powered systems [3], [4]. As a result, a redundant approach at both the logic design and the device levels has been applied.

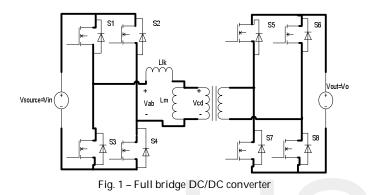

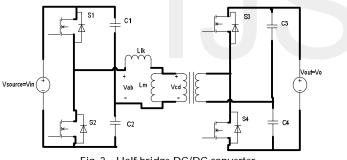

Fig. 2 – Half bridge DC/DC converter

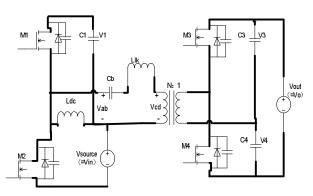

Fig. 3 – New half bridge DC/DC converter

Fig.4. Basic schematic of a digitally controlled boost converter

As shown in Fig. 1.b, the outputs of two identical logic blocks inside each FPGA are continuously compared to each other using an XNOR gate. An error in either logic block due to a SEU in a user register or a SEFI in the related configuration bits will deactivate the tri-state output buffers of the FPGA. Consequently, the failed device goes in an offline status in which all its outputs are in a high impedance state. A temporary data upset due to an SEU in a user register will quickly disappear, and the two logic blocks will resynchronize. However, a configuration bit SEFI will result in continuous disagreement between the two logic blocks. The remaining FPGA continues to generate the correct outputs, so that the continuous operation of the overall system is guaranteed.

The recovery from an error condition due to a SEFI is achieved by a cross-checking procedure. Each FPGA continuously monitors the operating state of the other FPGA. If an incorrect operating condition is detected, the failed device is reconfigured. The SEFI detection can be performed by reading back the actual configuration data and comparing it with the original configuration bit-stream. However, this approach relies on a particular feature available only on Vertex FPGAs [6]. A more general approach was applied based on the detection of the offline status of an FPGA through the use of a watchdog counter. The expiring counting value can be set so that an error due to a temporary upset, such as a user register flip, does not force the reconfiguration of the FPGA.

Unfortunately, a reconfiguration alone is not sufficient to restore the system to full functionality because the two FPGAs must resynchronize their current operating states. The simplest way to achieve this is by means of a general reset. However, a reset will disrupt the current state of the system, and an undesirable transient pulse will result at the DC/DC converter output. To avoid this transient error, the logic block was designed so that the reconfigured device can load the current state of the system from the device that is still operating.

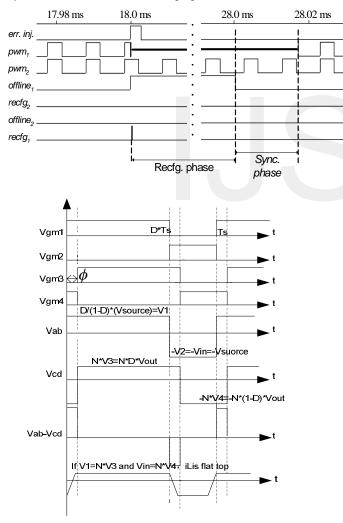

In order to validate this approach a proof-of-concept demonstration was implemented using Altera FPGAs from the FLEX10K family. An error injection block is used to simulate the occurrence of an error into a logic block, and a reconfiguration emulator block is used to emulate the reconfiguration phase. The reconfiguration emulator module forces the output of the related device to a high impedance state during the configuration period, and at its end forces a reset of the device. Fig. 1.a shows the VHDL simulation of the overall system. Note that after the injection of an error in the first FPGA, the second FPGA detects the incorrect status of the first device through the offline signal and forces its reconfiguration. During the reconfiguration and the resynchronization phases, the second device generates the correct PWM waveform, and at the end of those phases the reconfigured device restarts operation with the correct duty cycle.

Fig. 1. simulation of the overall system

# CONCLUSION

This work demonstrates the design of a digitally controlled boost converter suitable for space applications based on an SRAM FPGA. A RHBD technique has been developed and applied to assure the continuous operation of the converter in the presence of SEEs (more precisely SEFIs) that can occur in the FPGA device. This technique utililizes redundant logic combined with a non-disruptive procedure to resynchronize the two devices after a reconfiguration. The proposed approach has successfully been validated through both VHDL simulations and experiments performed а proof-of-concept on demonstrator using off-the-shelf FPGA constructed devices.

## REFERENCES

- A. Capel, D. O'Sullivan, J. C. Marpinard, "High-Power Conditioning for Space Applications," *Proc. of the IEEE*, vol. 76, no. 4, pp. 391-408, Apr. 1998.

- [2] T. W. Martin, S. S. Ang, "Digital control for switching converters," *Proc. of IEEE Int. Symp. on Industrial Electronics*, ISIE'95, vol. 2, pp. 480-484, July 1995.

- [3] C. Barillot, J. P. Calvel, P. Poirot, "Total dose and heavy ions evaluation of UC1806 pulse width modulator from Unitrode," *Proc. of IEEE Radiation Effects Data Workshop*, NSREC, pp. 55-59, July 1995.

- [4] P. C. Adell, R. D. Schrimpf, B. K. Choi, W. T. Holman, J. P. Attwood, C. R. Cirba, K. F. Galloway, "Total-Dose and Single-Event Effects in Switching DC/DC Power converter," IEEE Trans. Nucl. Sci., vol. 49, no. 6, pp. 3217-3221, Dec. 2002.

- [5] M. Bellato, M. Ceschia, M. Menichelli, M. Papi, J. Wyss, A. Paccagnella, "Ion beam testing of SRAM-based FPGA's," *Proc. of Radiation and Its Effects on Components and Systems conference*, RADECS, pp. 458-461, Sept. 2001.

- [6] C. Carmichael, E. Fuller, P. Blain, M. Caffrey, "SEU Mitigation Techniques for Virtex FPGAs in Space Applications," *Proc. of 2<sup>nd</sup> MAPLD International Conference*, Sept. 1999.

- [7] J. Roh, S. D. Lee, S. Park, "Digital PWM controller for DC-DC converters with minimum analogue circuits," *Electronics letters*, vol. 39, no. 19, pp. 1402-1403, Sept. 2003.

- [8] Mahdi Mozaffari Legha, "Determination of exhaustion and junction of in distribution network and its loss maximum, due to geographical condition", MS.c Thesis; Islamic Azad University, Saveh Branch, Markazi Province, Iran; pp. 1-300, Aug 2011.

- [9] Mahdi Mozaffari Legha, Rouhollah Abdollahzadeh, Ardalan Zargar, Mostafa Shadfar. "Effective method for optimal allocation of distributed generation units in radial electric power systems by genetic algorithm and imperialist competitive algorithm", International Journal on Technical and Physical Problems of Engineering (IJTPE), Issue 15, Vol. 5, No. 2, pp. 70-74, June 2013.

- [10] Mahdi Mozaffari Legha, Moein khosravi, Mohammad Hossein Armand, Mahdiyeh Azh,, "Optimization of Location and Capacity DGs Using HPSO Approach Case Study on the Electrical Distribution Network of north Kerman Province", Middle-East Journal of Scientific Research, pp. 461-465, 2013.

- [11] Mahdi Mozaffari Legha,; "Optimal Conductor Selection of Radial Distribution Networks Using GA Method" CIRED Regional – Iran, Tehran, 13-14 Jan 2013; Paper No: 12-F-500-0320.

International Journal of Scientific & Engineering Research, Volume 5, Issue 10, October-2014 ISSN 2229-5518 905

- [12] Mahdi Mozaffari Legha, Farzaneh Ostovar, "Analysis and Reconductoring of Overhead Conductors with Considering aging for Radial Distribution Systems Using Imperialist competitive Algorithm", International Journal of Pure and Applied Sciences and Technology, Vol. 20, No. 1, January 2014, pp. 1-8.

- [13] Mahdi Mozaffari Legha, Houman Gadari1,, "Technical and Economical Evaluation of Solar Plant for Electricity Supply Anar City Residential Customers", Middle-East Journal of Scientific Research, pp. 455-460, 2013.

- [14] Mahdi Mozaffari Legha, Mohammad Mohammadi; Aging Analysis and Reconductoring of Overhead Conductors for Radial Distribution Systems Using Genetic Algorithm; Journal of Electrical Engineering & Technology (JEET); pp. 1-8, 2014.

- [15] Mahdi Mozaffari Legha,;"Optimal Conductor Selection of Radial Distribution Networks Using GA Method" CIRED Regional – Iran, Tehran, 13-14 Jan 2013; Paper No: 12-F-500-0320.

- [16] Mahdi Mozaffari Legha, Hassan Javaheri, Mohammad Mozaffari Legha, "Optimal Conductor Selection in Radial Distribution Systems for Productivity Improvement Using Genetic Algorithm "Iraqi Journal for Electrical and Electronic Engineering (IJEEE), Vol.9 No.1, 2013, 29-36.

- [17] Mahdi Mozaffari Legha and et al, "A new hybrid particle swarm optimization approach for sizing and placement enhancement of distributed generation" IEEE Conference, 2155-5516; Pages 1277 - 1281.

- [18] Web site Electrical Power Engineering Specialists, REPORTs, 2014. Available at: <http://www.drmozaffarilegha.ir> [accessed 01.01.2014]

- [19] Mahdi Mozaffari Legha Majid Gandomkar, "Reconfiguration of MV network for balancing and reducing losses to by CYMEDIST software in Khorramabad", 16th Electric Power Distribution Conference (EPDC16), pp. 25-32, 2012.

- [20] Mahdi Mozaffari Legha, Houman Gadari1,, "Technical and Economical Evaluation of Solar Plant for Electricity Supply Anar City Residential Customers", Middle-East Journal of Scientific Research, pp. 455-460, 2013.